Автор: Денис Аветисян

Новый подход позволяет создавать аналоговые и смешанные схемы, используя алгоритмы машинного обучения и обратную связь от симуляторов.

Представлена платформа AstRL, использующая обучение с подкреплением и графовые нейронные сети для автоматизированного проектирования аналоговых и смешанных схем.

Несмотря на постоянный рост сложности современных вычислительных и коммуникационных систем, автоматизация проектирования аналоговых и смешанных интегральных схем (AMS) остается серьезной проблемой. В данной работе представлена новая методика ‘AstRL: Analog and Mixed-Signal Circuit Synthesis with Deep Reinforcement Learning’, использующая обучение с подкреплением для автоматического синтеза AMS-схем путем формулирования процесса проектирования как генерации графа и использования обратной связи из симулятора для надежной оптимизации. Предложенный подход AstRL позволяет генерировать схемы, оптимизированные под заданные пользователем характеристики, и впервые демонстрирует экспертно-ориентированный подход к обобщенной генерации схем, подтвержденный в симуляции. Возможно ли дальнейшее расширение возможностей AstRL для решения еще более сложных задач проектирования и достижения новых уровней автоматизации в области AMS-схем?

Вызов Автоматизированного Проектирования AMS-Схем

Проектирование смешанных аналого-цифровых схем (AMS Circuit Design) по-прежнему представляет собой сложную задачу, требующую глубоких знаний и значительных временных затрат. В отличие от цифрового проектирования, где автоматизация достигла значительных успехов, аналоговая часть требует учета множества взаимосвязанных параметров и компромиссов, что делает процесс крайне трудоемким. Квалифицированные инженеры тратят месяцы на разработку, моделирование и оптимизацию даже относительно простых схем, чтобы обеспечить соответствие заданным требованиям по производительности, энергопотреблению и надежности. Данная сложность замедляет темпы инноваций и ограничивает возможности быстрого прототипирования, что особенно критично в условиях современной быстро меняющейся электроники.

Традиционные методы разработки аналого-цифровых смешанных сигнальных схем (AMS) сталкиваются с растущей сложностью одновременной оптимизации ключевых параметров производительности и соблюдения физических ограничений. Проектирование, требующее учета множества взаимосвязанных факторов, таких как энергопотребление, скорость, точность и площадь кристалла, часто приводит к компромиссам и длительным циклам итераций. Попытки оптимизировать один аспект схемы нередко приводят к ухудшению других, что вынуждает инженеров вручную балансировать эти противоречия. С увеличением плотности интеграции и усложнением топологии схем, эта задача становится все более трудоемкой и требует значительных временных затрат, ограничивая скорость инноваций и увеличивая стоимость разработки.

Существующие автоматизированные инструменты для проектирования аналого-цифровых смешанных схем (AMS) зачастую демонстрируют недостаточную гибкость и эффективность применительно к современным требованиям. Это связано с тем, что традиционные подходы, как правило, ориентированы на оптимизацию отдельных параметров, не учитывая при этом сложные взаимосвязи между различными элементами схемы и физические ограничения, накладываемые технологическим процессом. В результате, проектировщикам приходится тратить значительное время на ручную доработку результатов, полученных с помощью автоматизированных средств, что существенно замедляет процесс инноваций и повышает стоимость разработки. Ограниченность существующих инструментов препятствует созданию высокопроизводительных и энергоэффективных схем, необходимых для современных приложений, таких как искусственный интеллект, беспроводная связь и медицинская электроника.

Ограниченность существующих подходов к автоматизированному проектированию аналого-цифровых систем (AMS) обуславливает необходимость принципиально новой парадигмы генерации схем. Традиционные методы, ориентированные на последовательную оптимизацию отдельных параметров, оказываются неэффективными при работе со сложными современными задачами, где критически важен одновременный учет множества характеристик и физических ограничений. Поэтому все больше внимания уделяется концепциям, основанным на алгоритмах эволюционного поиска и машинном обучении, позволяющим исследовать широкий спектр возможных решений и находить оптимальные конфигурации, удовлетворяющие заданным требованиям. Такой подход, в отличие от ручной настройки и последовательной оптимизации, открывает возможности для создания высокопроизводительных и энергоэффективных схем, значительно сокращая время разработки и снижая риски, связанные с человеческим фактором.

AstRL: Графовый Подход к Обучению с Подкреплением

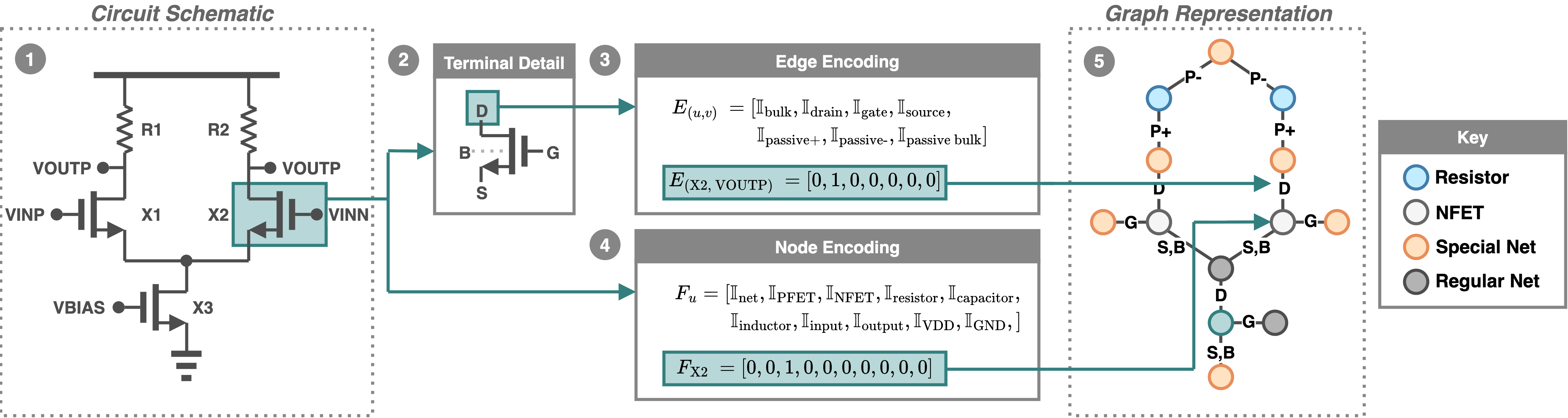

В AstRL топологии электрических цепей представлены в виде графов, где узлы соответствуют компонентам, а ребра — соединениям между ними. Такое графовое представление позволяет внедрить структурные априорные знания (structural inductive biases), отражающие типичные особенности схем, что существенно ускоряет процесс обучения. Использование графов обеспечивает эффективное кодирование информации о связях между компонентами и позволяет алгоритму обобщать знания на новые, ранее не встречавшиеся топологии. Кроме того, графовое представление облегчает применение алгоритмов, разработанных для работы с графовыми данными, что повышает эффективность обучения и снижает вычислительные затраты.

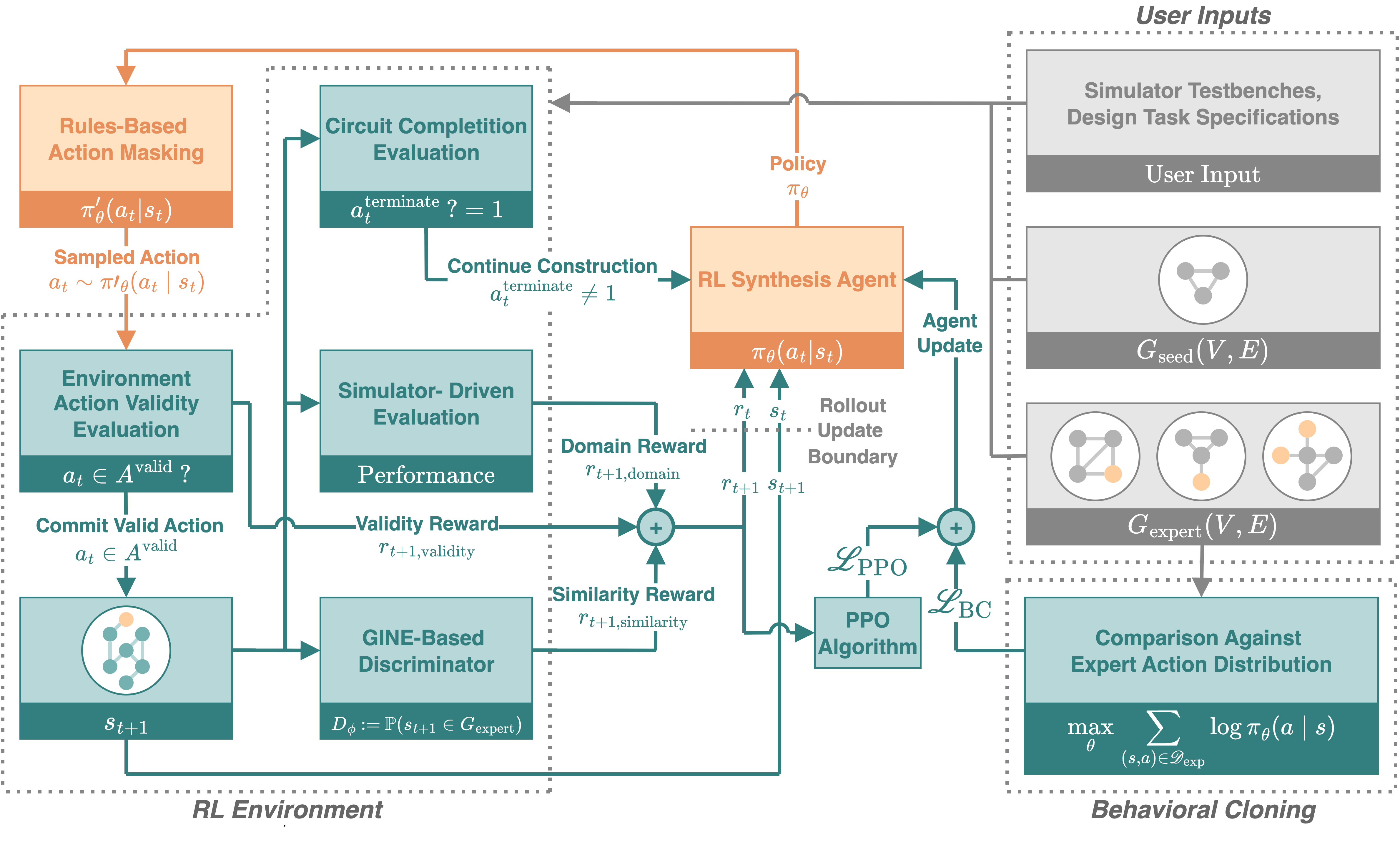

В основе AstRL лежит метод обучения с подкреплением, использующий градиентную политику для последовательной генерации графов, представляющих электронные схемы. В процессе обучения агент, основанный на градиентной политике, итеративно формирует структуру схемы, добавляя или удаляя компоненты и соединения. Целью является максимизация целевых показателей производительности, таких как задержка, энергопотребление и площадь кристалла. Алгоритм оптимизирует параметры политики, направляя процесс генерации графов таким образом, чтобы формировать схемы, которые достигают наилучших результатов по заданным метрикам. В процессе оптимизации используется стохастический градиентный спуск для обновления параметров политики на основе полученных вознаграждений.

Система AstRL использует разработанную функцию вознаграждения для управления процессом обучения, обеспечивая баланс между тремя ключевыми компонентами. Во-первых, учитывается достоверность симуляции — вознаграждение увеличивается при приближении результатов моделирования к физически правдоподобным значениям. Во-вторых, оценивается соответствие полученной схемы заданным спецификациям, таким как требуемые частотные характеристики или потребляемая мощность. Наконец, функция вознаграждения штрафует за чрезмерную сложность схемы, стимулируя генерацию более компактных и эффективных решений. Комбинирование этих трех факторов позволяет системе оптимизировать топологию схемы с учетом как функциональных требований, так и практических ограничений.

В системе AstRL используется метод поведенческого клонирования (Behavioral Cloning) для ускорения обучения и повышения начальной производительности. Этот метод заключается в обучении агента путем имитации действий эксперта, представленных в виде набора демонстраций. Вместо обучения с нуля методом проб и ошибок, AstRL изначально обучается на данных, полученных от эксперта в области проектирования схем, что позволяет агенту быстрее освоить базовые принципы и стратегии. Поведенческое клонирование используется как этап предварительного обучения, после которого применяется обучение с подкреплением для дальнейшей оптимизации и адаптации к новым задачам. Это позволяет значительно сократить время обучения и улучшить качество генерируемых схем на ранних этапах.

Обеспечение Корректности и Оптимизации Генерируемых Схем

При построении графа схемы, мы применяем структурные ограничения для обеспечения корректности и физической реализуемости топологии схемы. Эти ограничения включают в себя правила, касающиеся типов соединений между элементами, допустимых конфигураций узлов и соблюдения технологических ограничений, таких как минимальная ширина проводников и расстояния между ними. Применение данных ограничений на этапе построения графа позволяет исключить невалидные или нереализуемые схемы на ранних стадиях процесса проектирования, существенно снижая вычислительные затраты и гарантируя, что сгенерированные схемы соответствуют требованиям производственного процесса и физическим законам.

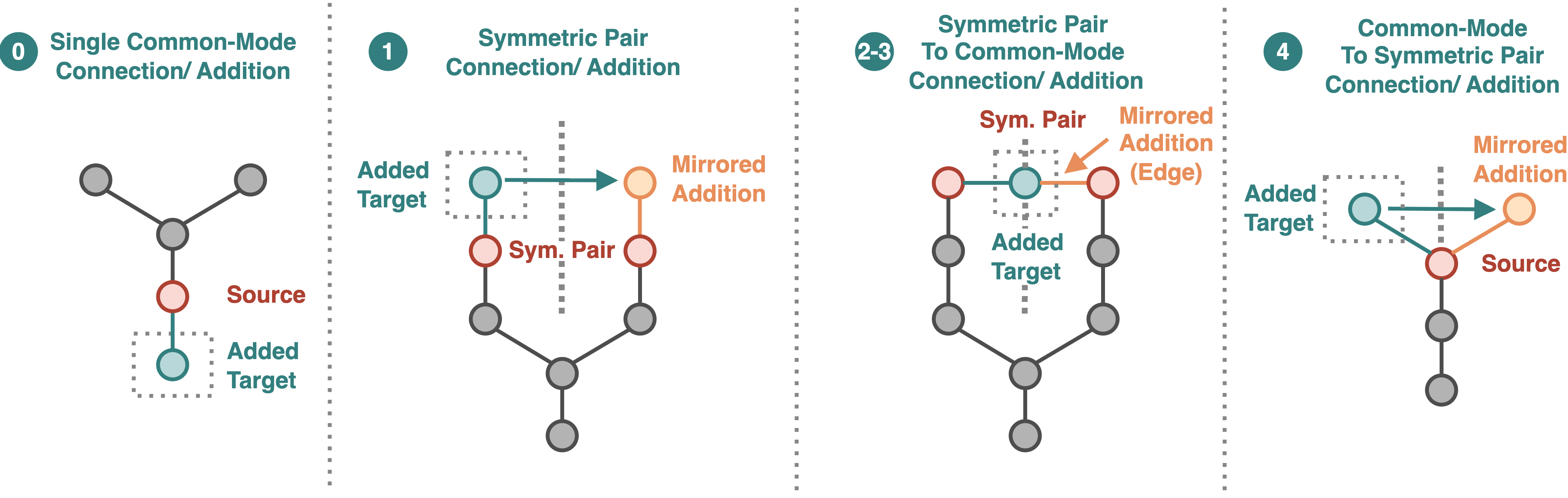

Для повышения производительности и снижения пространства поиска при генерации схем используются симметричные модификаторы действий (Symmetric Action Modifiers). Эти модификаторы направлены на продвижение симметрии в структуре разрабатываемых схем. Применение симметрии позволяет уменьшить количество уникальных компонентов и соединений, которые необходимо рассматривать в процессе поиска оптимального решения. Это достигается путем ограничения пространства поиска только теми конфигурациями, которые обладают определенной степенью симметрии, что значительно ускоряет процесс генерации и снижает вычислительную сложность. Использование симметрии также может привести к созданию более устойчивых и надежных схем, поскольку симметричные структуры часто обладают лучшими характеристиками устойчивости к шумам и отклонениям параметров компонентов.

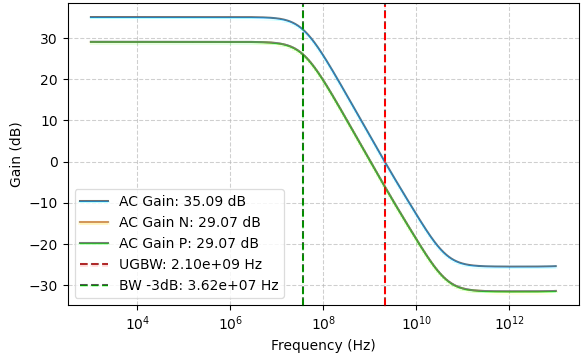

Оценка предложенного фреймворка AstRL проводилась с использованием технологического процесса Skywater 130nm, являющегося индустриальным стандартом для моделирования и изготовления интегральных схем. Данный процесс обеспечивает доступность проверенных библиотек компонентов и моделей, необходимых для точной оценки производительности генерируемых схем. Использование Skywater 130nm позволяет проводить верификацию разработанных схем с точки зрения физической реализуемости и соответствия требованиям технологического процесса, а также обеспечивает возможность дальнейшего прототипирования и изготовления реальных чипов.

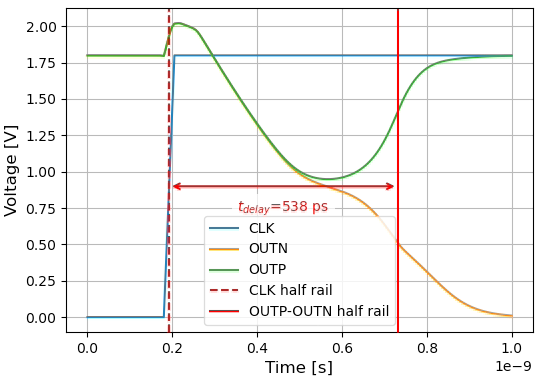

В ходе оценки AstRL успешно генерировались разнообразные схемы, включая операционные усилители (OTA), компараторы и кольцевые генераторы, при этом 100% сгенерированных списков соединений (netlists) оказались синтаксически корректными и пригодными для дальнейшего моделирования и изготовления. Это подтверждает работоспособность предложенного подхода к генерации схем и его способность создавать функциональные и валидные топологии для различных типов аналоговых блоков.

В ходе сравнительного анализа предложенный фреймворк продемонстрировал значительное улучшение показателей как валидности симуляции, так и соответствия техническим требованиям по сравнению с существующими передовыми методами. В частности, наблюдалось увеличение процента успешно сгенерированных и корректно симулируемых схем, а также повышение степени выполнения заданных спецификаций по ключевым параметрам, таким как потребляемая мощность и скорость работы. Данное улучшение достигнуто за счет комплексного подхода, включающего структурные ограничения и симметричные модификаторы действий, что позволяет создавать более надежные и оптимизированные схемы.

Расширяя Горизонты: Будущее Автоматизированного Проектирования Схем

Разработанная платформа AstRL значительно расширяет возможности существующих методов автоматизированного проектирования аналоговых схем, таких как AnalogCoder и AnalogGenie. В отличие от предшественников, AstRL использует подход, основанный на обучении с подкреплением, что позволяет ей генерировать схемы с превосходящими характеристиками и большей эффективностью. Экспериментальные данные демонстрируют, что AstRL не только превосходит существующие инструменты в задачах оптимизации ключевых параметров схем, но и способна находить решения, недостижимые при использовании традиционных методов. Это достигается за счет способности платформы исследовать более широкое пространство возможных решений и адаптироваться к сложным ограничениям, что открывает новые перспективы для создания высокопроизводительных и энергоэффективных аналоговых систем.

Адаптивность разработанного фреймворка открывает возможности для беспрецедентно быстрой разработки прототипов и исследования новых архитектур электронных схем. Благодаря гибкой структуре, система позволяет инженерам оперативно генерировать и тестировать различные варианты схем, значительно сокращая время, необходимое для итераций и оптимизации. Это особенно ценно при разработке специализированных схем или исследовании принципиально новых подходов к проектированию, когда традиционные методы оказываются слишком трудоемкими. Возможность быстрого прототипирования стимулирует инновации, позволяя специалистам смело экспериментировать с различными концепциями и оперативно оценивать их практическую реализуемость, тем самым ускоряя процесс создания передовых электронных устройств.

Автоматизированное проектирование электронных схем обладает огромным потенциалом для существенного сокращения сроков разработки и ускорения инноваций в различных областях. Традиционный процесс, требующий значительных временных затрат и экспертных знаний, может быть радикально оптимизирован за счет использования алгоритмов автоматического синтеза. Это позволяет инженерам сосредоточиться на более сложных задачах, таких как определение требований к системе и верификация разработанных решений, вместо рутинной работы по трассировке соединений и выбору компонентов. В результате, создание новых устройств и систем может происходить в разы быстрее, что особенно важно в быстроразвивающихся областях, таких как телекоммуникации, медицина и искусственный интеллект. Потенциал автоматизации простирается от проектирования аналоговых и цифровых микросхем до разработки печатных плат и систем на кристалле, открывая новые возможности для создания более эффективных, компактных и доступных электронных устройств.

В дальнейшем планируется расширить возможности разработанной системы за счет включения более сложных ограничений при проектировании схем. Исследователи стремятся к оптимизации не только базовых характеристик, но и дополнительных показателей производительности, таких как энергоэффективность, устойчивость к помехам и компактность. Это позволит создавать схемы, отвечающие специфическим требованиям различных приложений, от высокопроизводительных вычислений до маломощных мобильных устройств. Особое внимание будет уделено автоматической верификации разработанных схем на соответствие заданным критериям, что значительно повысит надежность и качество конечного продукта. Реализация этих усовершенствований откроет новые горизонты в области автоматизированного проектирования электронных схем и позволит существенно ускорить инновационные процессы.

Представленная работа демонстрирует элегантность подхода к автоматизации проектирования аналоговых и смешанных схем. AstRL, формируя процесс проектирования как генерацию графа, позволяет создавать сложные системы, опираясь на обратную связь от симуляторов. Этот метод, по сути, признает, что хорошая система — живой организм, где нельзя исправить одну часть, не понимая целого. Тим Бернерс-Ли однажды сказал: «Веб — это не просто набор страниц, связанных гиперссылками, а способ думать». Подобно тому, как веб соединяет разрозненные элементы в единое целое, AstRL объединяет этапы проектирования, позволяя создавать схемы с оптимизированной топологией и надежными характеристиками. Модульность, реализованная в AstRL через генерацию графов, действительно эффективна, поскольку учитывает контекст, а не стремится к иллюзии контроля.

Куда Далее?

Представленная работа, безусловно, демонстрирует потенциал обучения с подкреплением в автоматизированном проектировании аналого-смешанных схем. Однако, элегантность решения не должна заслонять присущие ему компромиссы. Генерация топологии, хоть и достигнута, остаётся процессом, требующим тонкой настройки функции вознаграждения. Каждое упрощение в этой настройке неизбежно влечёт за собой потерю в оптимизации конкретных параметров схемы, а каждая изощрённость — риск переобучения и снижения обобщающей способности.

Перспективы дальнейших исследований, по всей видимости, лежат в области более глубокого понимания взаимосвязи между структурой графа представления схемы и её функциональными характеристиками. Симметрия, как фактор, учтенный в данном исследовании, — лишь один из аспектов. Более того, необходимо разработать методы, позволяющие учитывать ограничения, накладываемые технологическим процессом, непосредственно на этапе генерации графа, а не на этапе постобработки.

В конечном счёте, задача автоматизированного проектирования схем — это не просто поиск оптимальной топологии, но и создание системы, способной адаптироваться к изменяющимся требованиям и ограничениям. Истинный прогресс, вероятно, будет достигнут не за счёт увеличения сложности алгоритмов, а за счёт их упрощения и повышения степени понимания фундаментальных принципов, определяющих поведение аналоговых и смешанных схем.

Оригинал статьи: https://arxiv.org/pdf/2602.12402.pdf

Связаться с автором: https://www.linkedin.com/in/avetisyan/

Смотрите также:

- ПРОГНОЗ ДОЛЛАРА К ШЕКЕЛЮ

- БИТКОИН ПРОГНОЗ. BTC криптовалюта

- SIREN ПРОГНОЗ. SIREN криптовалюта

- MYX ПРОГНОЗ. MYX криптовалюта

- ЭФИРИУМ ПРОГНОЗ. ETH криптовалюта

- SOL ПРОГНОЗ. SOL криптовалюта

- SAROS ПРОГНОЗ. SAROS криптовалюта

- ZEC ПРОГНОЗ. ZEC криптовалюта

- ПРОГНОЗ ДОЛЛАРА

- ДОГЕКОИН ПРОГНОЗ. DOGE криптовалюта

2026-02-16 10:32